Combating the Reliability Challenge of GPU Register File at Low Supply Voltage | Proceedings of the 2016 International Conference on Parallel Architectures and Compilation

![Towards Microarchitectural Design of Nvidia GPUs — [Part 1] | by Dung Le | Distributed Knowledge | Medium Towards Microarchitectural Design of Nvidia GPUs — [Part 1] | by Dung Le | Distributed Knowledge | Medium](https://miro.medium.com/max/1200/0*4yZTZIBxx5lDAs3o.png)

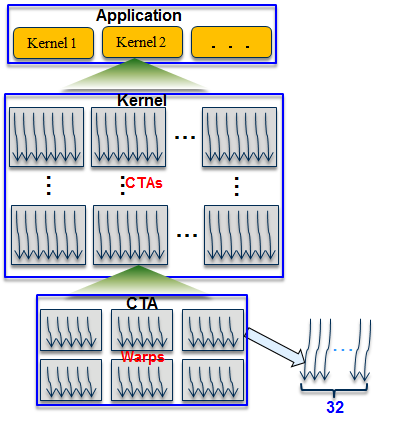

Towards Microarchitectural Design of Nvidia GPUs — [Part 1] | by Dung Le | Distributed Knowledge | Medium

![PDF] GPU chip Select Register File Pending Warps ALUs Cache / Scratch Banks ( 32 x 2 KB ) | Semantic Scholar PDF] GPU chip Select Register File Pending Warps ALUs Cache / Scratch Banks ( 32 x 2 KB ) | Semantic Scholar](https://d3i71xaburhd42.cloudfront.net/d786d4c7b9db8db7aff7ea3be5f311712d7c6333/2-Figure1-1.png)

![PDF] Performance-centric register file design for GPUs using racetrack memory | Semantic Scholar PDF] Performance-centric register file design for GPUs using racetrack memory | Semantic Scholar](https://d3i71xaburhd42.cloudfront.net/0063e4afef59c2342733b2895e231a4e8e88c516/2-Figure1-1.png)